# Interoperability of EFCI and ER Switches for ABR Services in ATM Networks

Yuan-Cheng Lai and Ying-Dar Lin National Chiao Tung University

#### **Abstract**

With the advances in switching technologies, ER switches are becoming popular since they perform better than EFCI switches. In the transitional period, EFCI and ER switches may coexist in the same ATM network. Hence, the efficiency of various ER schemes should be reevaluated in the mixed EFCI-ER environment, not only in the homogeneous ER environment. Also, some important implications are observed in the heterogeneous environments. Because the location of an ER switch in the topology is critical to its performance, some placement rules, which describe how to place the ER switches for network operators, are developed in order to achieve a better performance of the network. In summary, the results presented here should serve as an operational reference for service providers.

synchronous transfer mode (ATM) is the most promising transfer technology for implementing the broadband integrated services digital network (B-ISDN). It supports applications with distinct quality of service (QoS) requirements such as delay, jitter, and cell loss, and distinct demands such as bandwidth and throughput, so it can enable multimedia communication over the networked environment. However, in order to support old applications or some applications that do not choose to use performance-guaranteed services, an ATM network also provides best-effort services such as LAN emulation and IP-over-ATM. To provide these services for a wide variety of applications, the ATM Forum has defined a family of service categories including constant bit rate (CBR) service, real-time variable bit rate (rt-VBR), non-real-time VBR (nrt-VBR), unspecified bit rate services (UBR), and available bit rate (ABR) service [1].

As we know, ABR service is suited for a wide variety of applications since it can support data traffic economically [2]. However, when these applications, such as IP-over-ATM, transmit data packets in ATM networks, they segment each packet into ATM cells. The loss of any cell causes the retransmission of the entire packet. Under the condition of congestion, throughput collapses since too many packet retransmissions result from cell loss [3]. Hence, it is necessary to adopt some congestion methods to decrease cell loss and increase throughput.

Recently, some feedback flow control schemes have been

presented in order to provide ABR services [4–11]. Two strategies have been proposed: credit-based [4, 5] and rate-based [2, 6–11]. The credit-based scheme is a link-by-link window flow control scheme. Each link in the network independently runs the flow control mechanism. The rate-based scheme uses the feedback signal from the network to control the rate at which each source transmits cells into the network. In late 1994, the ATM Forum voted for rate-based control as ABR service.

In traffic management specification TM 4.0, the detailed and concise operations of rate-based flow control are described. The behavior of traffic sources and destinations is clearly defined in order to provide the baseline for vendors to follow. However, the methods the switches use to control the source rate are up to the vendors. Currently, most ATM vendors have already provided ATM switches equipped with explicit forward congestion indication (EFCI) functions recommended by the International Telecommunication Union — Telecommunication Standardization Sector (ITU-T) [12]. These switches, which use EFCI marking, are called first-generation switches [13]. With the advances in switching technologies, second-generation switches, which have the explicit rate (ER) setting capacity, are becoming popular.

In the transitional period from first- to second-generation switches, interoperation of EFCI and ER switches becomes unavoidable. Because of the differences in their basic operations, whether they can cooperate efficiently ialong the path of

the same virtual circuit (VC) is questionable. In this article, the performance of interoperating various ER schemes with EFCI is presented and compared. Although we know some properties of these ER schemes from many papers [2, 6–11], the knowledge is obtained from an environment in which all switches use the same flow control algorithm. However, from our simulation, the behavior of these ER schemes in a mixed EFCI-ER environment is sometimes different from that in a pure ER environment. Hence, these ER schemes must be reevaluated.

In a mixed EFCI-ER environment, the location of ER is a critical issue for performance. When a customer buys a switch equipped with an ER setting capacity, which EFCI switch should be replaced first to obtain the best performance? We performed some simulations with various network configurations. The simulation results provide important implications on which EFCI switches to be replaced. Therefore, from our results the network operators can have better insight to help themselves purchase proper ER switches to fit their needs. Also when they are about to install their ER switches, they can choose the appropriate EFCI switches to be replaced.

The remainder of this article is organized as follows. In the second section, we describe the operations of EFCI switches and various ER switches. Simulation environments are presented in the third section. In the fourth section, we present and discuss simulation results obtained in the homogeneous and heterogeneous EFCI-ER environments. Some guidelines for placing ER switches are given in the fifth section. The final section points out some future work.

# ABR Flow Control

First, we briefly introduce the basic operation of the closed-loop rate-based control mechanism [1]. When a VC is established, the source end system (SES) sends the cells at the allowed cell rate (ACR), which is set as the initial cell rate (ICR). In order to probe the congestion status of the network, the SES sends a forward resource management (RM) cell (Table 1) every  $N_{rm}-1$  data cells. Each switch may set certain fields of the RM cell to indicate its own congestion status or the bandwidth the VC source should use. The destination end system (DES) returns the forward RM cell as a backward RM cell to the SES. According to the received backward RM cell, the SES adjusts its ACR, which is bound between peak cell rate (PCR) and minimum cell rate (MCR).

The RM cell contains a 1-bit congestion indication (CI) set to zero, and an explicit rate (ER) field is set initially to PCR by the SES. When the SES receives a backward RM cell, it modifies its ACR using additive increase and multiplicative

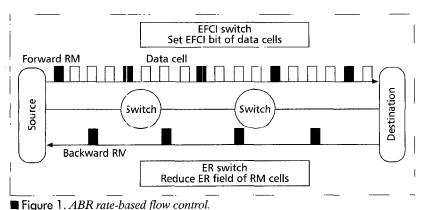

■ Figure 1. ABR rate-basea flow control.

|          |                                     | yva.<br>Suled |       |

|----------|-------------------------------------|---------------|-------|

| Header   | ATM header                          | 1–5           | All . |

| ID       | Protocol identifier                 | 6             | All   |

| DIR      | Message type: direction             | 7             | 8     |

| BIN      | Message type: BECN cell             | 7             | 7     |

| CI       | Message type: congestion indication | 7             | 6     |

| NI       | Message type: no increase           | 7             | 5     |

| RA       | Message type: request/acknowledge   | 7             | 4     |

| Reserved | Message type: reserved              | 7             | 3-1   |

| ER       | Explicit cell rate                  | 8-9           | All   |

| CCR      | Current cell rate                   | 10–11         | All   |

| MCR      | Minimum cell rate                   | 12–13         | All   |

| QL       | Queue length protocol identifier    | 14–17         | All   |

| SN       | Sequence number                     | 18–21         | All   |

| Reserved | Reserved                            | 22–51         | All   |

| Reserved | Reserved                            | 52            | 8–3   |

| CRC-10   | CRC-10                              | 52            | 21    |

| CRC-10   | CRC-10                              | 53            | All   |

■ Table 1. *Fields and their positions in RM cells.*

decrease. The new ACR is computed as follows, depending on CI and ER fields in RM cells:

$ACR = max(min(ACR + RIF \cdot PCR,ER),MCR)$ , if CI = 0,  $ACR = max(min(ACR \cdot (1 - RDF),ER),MCR)$ , if CI = 1,

where RIF is the rate increase factor and RDF is the rate decrease factor.

According to the congestion monitoring and feedback mechanism, various switch mechanisms can be classified into two types. One is the EFCI switch, the other the ER switch. The components of rate-based flow control are shown in Fig. 1.

#### EFCI Scheme

In this scheme [14], when congestion occurs the switch sets the EFCI bit to one (EFCI = 1) in the header of each passing data cell. The DES, if a cell with EFCI = 1 has been received, marks the CI bit (CI = 1) to indicate congestion in each backward RM cell. In most cases, the queue length is used to decide whether congestion occurs or not. As the queue length

exceeds a threshold, denoted  $Q_t$ , congestion is claimed. When the queue length falls below the threshold, congestion is relieved.

#### Explicit Rate Feedback Schemes

In ER schemes, the switch computes the fair share of bandwidth with which a VC can be supported, and determines the load and the actual explicit rate. When each RM cell passes, the switch sets the ER field to the determined explicit rate. Note that each switch is not allowed to increase the ER field. Thus, a source shall receive the allowed MCR of all the switches along the path. Examples of ER switch mechanisms are the EPRCA, ERICA, CAPC, Charny Max-Min, and Tsang Max-Min schemes [15–19].

Enhanced Proportional Control Algorithm (EPRCA) [15] — Each switch maintains a mean allowed cell rate (MACR) using a running exponential weighted average. When a switch receives a forward RM cell during the congestion period, MACR is updated as

$$MACR = (1 - \alpha)MACR + \alpha CCR,$$

where  $\alpha$  is the exponential averaging factor generally set to be 1/16 and CCR is the current cell rate of the VC recorded in the RM cell. The fair bandwidth share is computed as a fraction of the MACR:

Fair share =

$$DPF \cdot MACR$$

,

where DPF is a switch downpressure factor set close to but below 1. When a switch receives a backward RM cell, it reduces the ER field to the fair share if its queue length is larger than  $Q_t$ .

Explicit Rate Indication for Congestion Avoidance (ERICA) [16] — ERICA uses a load factor, z, to indicate the overload or underload state of the switch. The load factor is defined as

$$z = \frac{\text{Input rate}}{\text{Target rate}}.$$

The input rate is measured over a fixed averaging interval, and the target rate is usually set slightly below

the link bandwidth. Because the goal of this algorithm is to maintain the load factor close to one, the sources ought to change their current sending rates inversely proportional to the calculated load factor. The VC share and fair share are as follows:

lows:

$$VC \text{ share} = \frac{CCR}{z},$$

Fair share =

$$\frac{Target \text{ rate}}{Number \text{ of active connections}}$$

A switch updates the ER field in the backward RM cell it received to the maximum value of the fair share and VC share.

Congestion Avoidance Using Proportional Control (CAPC) [17] — Again, as in the ERICA scheme, the switches set a target utilization slightly below 1 and compute the load factor. The main difference lies in the way the fair share is computed, which depends on whether z < 1 or z > 1. Thus, we have

Fair share = Fair share

$$\cdot \min(\text{ERU}, 1 + (1-z) \cdot R_{up})$$

, if  $z < 1$ , and

Fair share = Fair share

$$\cdot \max(ERF, 1 - (z - 1 \cdot R_{dn}), if z > 1$$

.

where  $R_{up}$  is a slope parameter between 0.025 and 0.1, and  $R_{dn}$  is between 0.2 and 0.8. ERU and ERF determine the maximum allowed increase and minimum allowed decrease, respectively. Usually ERU is set to 1.5 and ERF to 0.5. When

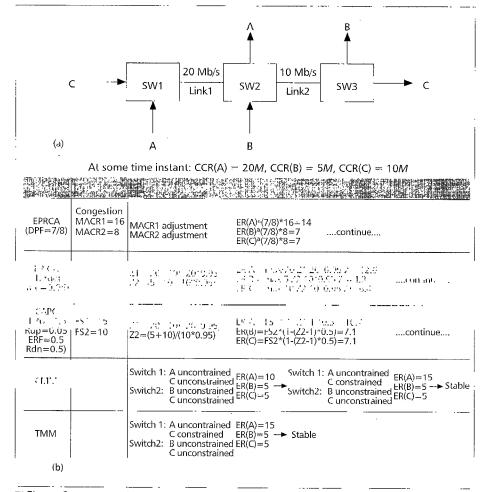

Figure 2. An example to explain the five ER schemes.

a returning RM cell arrives at the switch, the ER field is updated to the fair share.

The Charny Max-Min Scheme [18] — The fair share is computed using an iterative procedure in this scheme. Initially, the fair share is set to the link bandwidth divided by the number of active VCs. Some VCs cannot achieve the fair share at a switch because of the constraints imposed by the limited amount of bandwidth available at other switches along its path. For this switch, these VCs are called "constrained VCs." The switch can determine whether a VC is constrained or not by comparing the fair share with the CCR field in the received forward RM cell. If the CCR field is less than the fair share, the VC is a constrained VC. Otherwise, it is an unconstrained VC.

For high throughput, the available bandwidth which the constrained VCs cannot use should be utilized by the unconstrained VCs. Hence the fair share is computed as follows:

Fair share =

$$\frac{\text{Link bandwidth} - \sum \text{Bandwidth of constrained VCs}}{\text{Number of VCs} - \text{Number of constrained VCs}}$$

As a forward RM cell traverses the network, the switch determines whether the VC is constrained or not, recomputes the fair share, and reduces the ER and CCR fields of the RM cell down to their fair shares. The ER and CCR fields of a backward RM cell may be reduced further down to the most current fair share on the forward path.

The Tsang Max-Min Scheme (TMM) [19] — This scheme is similar to the Charny Max-Min method, except for three differences:

- The switch does not update the CCR field of the RM cell.

- The switch determines a VC state depending on the ER field, instead of the CCR field, of the RM cell.

- The switch determines the VC state and computes the fair share on forward and backward RM cells, not just the forward RM cell.

The following parameters are set for the above schemes in our example and simulation: Nrm = 32, PCR = 155 Mb/s, MCR = 0 b/s, ICR =

PCR/16, RIF = PCR/256, and RDF = 1/16. For EFCI, we used  $Q_t = 1000$  cells. For EPRCA, we set  $Q_t = 1000$  cells,  $\alpha$ = 1/16, and DPF = 7/8. Target rate is set to be 95 percent of the link bandwidth for EFICA and CAPC. Also, in the CAPC scheme we use the following parameters: ERU = 1.5,  $R_{up}$  = 0.05, ERF = 0.5, and  $R_{dn} = 0.5$ .

# An Example

We show a simple example to illustrate the operation of the five ER schemes described above. The example is shown in Fig. 2. The network configuration consists of three switches and three connections (A, B, C), as shown in Fig. 2 a. Connections A and B traverse a link, and C traverses two links. The operation of these schemes are exhibited in Fig. 2 b.

# Simulation Environments

We show the numerical results of these schemes in a homogeneous environment in which all switches utilize the same control scheme, and in a heterogeneous environment in which the switches utilize different control schemes. We first examine the network configuration and performance metrics.

# Network Configuration

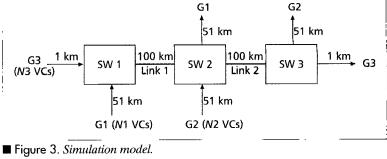

We use a simple three-switch configuration, as shown in Fig. 3, as our network topology. It is sufficient to exhibit the characteristics of various switches [20,21]. It consists of three

switches and some connections grouped into three groups (G1, G2, G3). G1 is the VCs traveling through link 1, only and Group 2 (G2) is the VCs traveling through link 2 only. Group 3 (G3) is the VCs passing through both links 1 and 2. There are N1, N2, and N3 connections in G1, G2, and G3, respectively. In our simulation, there are two VCs in each group (i.e., N1 = N2 = N3 = 2).

The link between two neighboring switches is 100 km long with 155 Mb/s capacity. For G3, the distance between a source and a switch is 1 km. On the other hand, the distance between a source and a switch is 51 km for G1 and G2. Hence, the propagation delay is the same for all groups. The reason is that we want to eliminate any unfairness caused by the different propagation delays. Also, all sources considered in the simulations are persistent.

#### Performance Metrics

The following performance measures are reported in the simulation.

Maximum Queue Length (MQL) — The maximum queue length is directly related to the cell loss probability when the buffer at the switch is finite. Also, we can observe the situation of ACR oscillation with this value. When this value is high, the ACR usually has larger oscillation.

Utilization (U) — From the value of utilization, we can know

how much bandwidth is wasted at the switch. Utilization is a clear measure of switch capacity.

Fairness (F) — Unfair behavior is observed from the value of fairness, which is defined as

$$F = \max(1 - \max(\text{all } |x_i - 1|), 0)$$

where  $x_i$  is the ratio of the actual throughput to the fair throughput for source i. This definition is the maximum ratio difference between ideal and achieved rates. We do not use the commonly used definition [2, 6, 8, 22],

$$F = \frac{\left(\sum x_i\right)^2}{n\sum x_i^2}$$

because only a few differences are observed. This is the major drawback of this metric.

As an example, we consider the case of 25 connections sharing the same bottleneck link in which bandwidth is 100 Mb/s. The fair solution is simply 4 Mb/s. If a scheme starves one connection completely and dis-

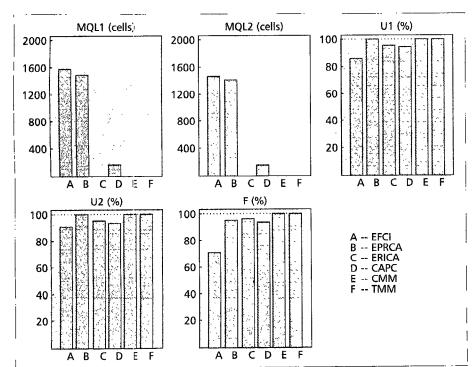

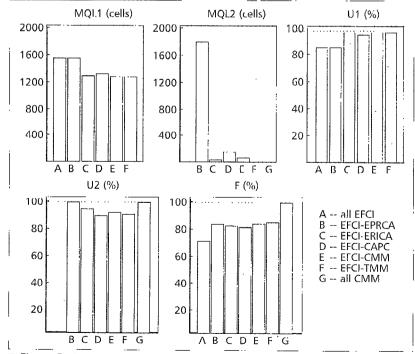

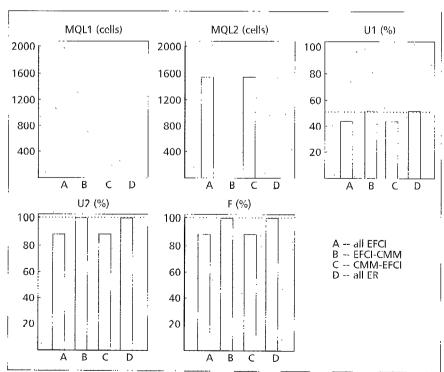

■ Figure 4. Comparison of the various switch schemes in homogeneous environments.

| EFCI | EFCI  | Using queue length                    | Simplicity                                       | High oscillation of ACR<br>High maximum queue length<br>Serious beat down problem                     |  |

|------|-------|---------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| ER   | EPRCA | Using MACR                            | Simplicity                                       | High oscillation of ACR<br>High maximum queue length<br>Beat down problem<br>Parameter tuning problem |  |

| ER   | ERICA | Using load factor and CCR             | Does not need per-<br>connection information     | Achieves target load<br>Sensitive to CCR errors                                                       |  |

| ER   | CAPC  | Using load factor and some parameters | Does not need per-<br>connection information     | Achievos target load<br>Parameter tuning problem                                                      |  |

| ER   | СММ   | Max-Min method<br>using CCR           | Oscillation-free<br>High utilization<br>Fairness | Needs per-connection information Sensitive to CCR errors                                              |  |

| ER   | TMM   | Max-Min method<br>using ER            | Oscillation-free<br>High utilization<br>Fairness | Needs per-connection<br>information<br>Sensitive to CCR errors                                        |  |

Itable 2. Comparison of the various switch schemes in homogeneous environments.

tributes its share evenly among other connections, the ratio value  $(x_1, x_2, ..., x_{24}, x_{25})$  is (100/96, 100/96, ..., 100/96, 0). The commonly used definition gives a fairness value of 96 percent, whereas the new metric gives 0, which appears more appropriate for the case of starvation.

# Numerical Results

#### Homogeneous Environment

Simulation results in the homogeneous environment are shown in Fig. 4. MQL1 and U1 represent the maximum queue length and utilization at switch 1. Similarly, MQL2 and U2 represent the maximum queue length and utilization at the switch 2. Note that the results about switch 3 are not shown because it does not become a bottleneck at any time

From the figure, it is obvious that the resulting behavior is more unfair in the homogeneous EFCI environment than in homogeneous ER environments. The main reason is that the beat down problem occurs when we use pure EFCI switches. The beat down problem is that VCs passing through a larger number of switches get less bandwidth than VCs passing through a smaller number of switches [2, 8, 22]. This effect is because VCs traveling more hops have a higher probability of getting their cells marked than those traveling fewer hops. As a result, it is likely that long-hop VCs cannot increase their rates, and consequently are beaten down by the short-hop VCs.

Also, we observe that the MQL of EFCI and EPRCA is large. This is caused by the large oscillation of ACR. Actually, in homogeneous environments the ACR of EFCI and EPRCA has large oscillation, the ACR of ERICA and CAPC has little oscillation, and the ACR of CMM and TMM is oscillation-free [9–11].

Regarding utilization, link capacity is not fully utilized because queue length threshold,  $Q_t$ , is set too low in the homogeneous EFCI environment. However, if  $Q_t$  is set high, the maximum queue length will be raised dramati-

cally [23, 24]. Hence, we sacrifice some bandwidth to keep the maximum queue length in the reasonable range. On the other hand, high utilization is achieved in the homogeneous ER environments. EPRCA has high utilization. ERICA and CPAC achieve the target rate. TMM and CMM utilize almost the complete link bandwidth. We summarize these results which are observed in the homogeneous environments as listed in Table 2.

The noticeable thing is that CMM and TMM are sensitive to CCR errors. This sensitivity does not depend on whether or not the CCR value is actually used by the algorithm, but rather on the fact that both schemes are purely computa-

tional algorithms with no rate measurements involved. It should be noted that this issue may be overcome by using rate measurements at the source.

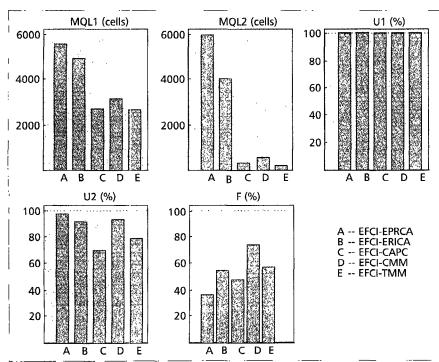

# Heterogeneous Environment

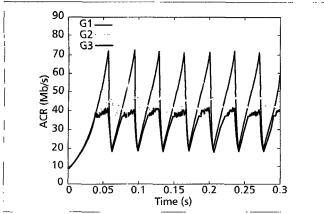

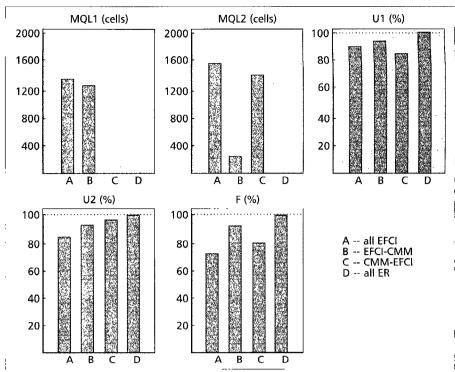

In this heterogeneous simulation we use an EFCI scheme on switch 1 and an ER scheme on switch 2. The results of interoperating EFCI with various ER schemes are illustrated in Fig. 5. In order to compare performance in the heterogeneous environment, we also plot the performance in the pure EFCI and pure CMM environments, denoted A and G, respectively. Also, Fig. 6 shows typical ACR dynamics in the EFCI-ER environment. From the results, we observe some important

Figure 5. Comparison of the various ER schemes in mixed EFCI-ER environments (RIF=1/256).

■ Figure 6. Typical ACR dynamics in the EFCI-ER environment.

implications which are not shown in the homogeneous environments.

The Beat Down Problem Exists when the EFCI Switch Appears — In the mixed EFCI-ER environment, the beat down problem still exists. This is due to the existence of the EFCI switch, as observed in Fig. 6. The ACR of VCs which pass EFCI and ER switches (G3) is not increased to a high level because it is restricted by ER switches. On the other hand, it must be decreased to a low level when congestion occurs in the EFCI switches. As a result, the beat down problem happens.

Actually, more EFCI switches cause a more severe beat down problem in ATM networks. On the other hand, more ER switches relieve the severity of the beat down problem.

Utilization of EFCI Switches Rises and Utilization of ER Switches Drops — From Fig. 5, this phenomenon is easily observed. Simply speaking, because EFCI switches own the high oscillation of ACR, they can easily grab the unused bandwidth. Hence, the utilization of EFCI switches rises. On the other hand, the low oscillation of ACR in ER switches causes a slow

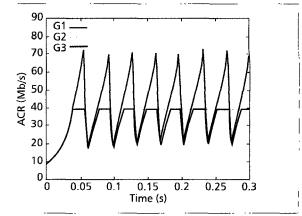

■ Figure 8. Comparison of the various ER schemes in the mixed EFCI-ER environments (RIF = 1).

■ Figure 7. ACR dynamics in the EFCI-TMM environment.

response to unused bandwidth. Therefore, much bandwidth is wasted, and the utilization of ER switches drops.

The CCR field in the RM Cells May Be Belated — In homogeneous ER environments, this condition happens rarely. However, in the mixed EFCI-ER environment, it occurs often. When congestion of the EFCI switch occurs (i.e., there are at least  $Q_t$  cells in the EFCI switch), the algorithm using the CCR field in the RM cells does not obtain the current cell rate because the RM cells are queued at the EFCI switch. Hence, the CCR fields of delayed RM cells are belated. As a result, the ER switch may use an inaccurate CCR field.

The ER Field Is Not Used in the RM Cells — TMM is a representative algorithm using the ER field in the RM cells. We can observe that the utilization of the TMM switch is low in the mixed EFCI-ER environments. As shown in Fig. 7, TMM does not obtain any ER information because the EFCI switch does not set the ER field. Hence, the scheme loses responsiveness. Therefore, we suggest

that all schemes do not use the ER information in the RM cells if EFCI switches may coexist.

The Value of RIF Should Not Be Set to a Large Value — Some papers use the high RIF to reduce the length of the transient period in the homogeneous ER environment [18–20]. When using the high RIF, the ACR of the source can quickly achieve the level of the ER field, regardless of the RIF value. Thus, the response time is reduced, especially for CMM or TMM

In order to understand the effect of RIF in the mixed EFCI-ER environment, we conducted the same simulation except with RIF = 1. The results are shown in Fig. 8. We observe that all EFCI switches must endure very large MQLs. Also, the EFCI switches are often in a congested state. We do not like to see this situation. On the other hand, ER switches do not obtain any benefit from that. All ER switches must endure larger MQLs. The utilization and fairness of all ER switches drop.

The Performance of CMM Is Better — Finally, the performance comparisons in the homogeneous and mixed environ-

| EPRCA | 1 | 1 | 1 | 5     | 5 | 5   | 5  | 5    | 5  |

|-------|---|---|---|-------|---|-----|----|------|----|

| ERICA | 4 | 2 | 3 | 3     | 2 | 4.  | 3  | 3    | 3. |

| CAPC  | 5 | 5 | 5 | 4     | 4 | 2   | 3  | 3    | 4  |

| СММ   | 2 | 3 | Z | 11.00 | 3 | 3 , | .1 | ., 1 | 2  |

| TMM   | 2 | 4 | 4 | 1     | 1 | 1   | 1  | 1    | 2  |

☐ Table 3. *Performance ranking of the various ER schemes in the homogeneous and mixed EFCI-ER environments.*

| Ideal                                | 51.83 | 25.92 | 25.92 | 100  |

|--------------------------------------|-------|-------|-------|------|

| All EFCI                             | 50.35 | 29.10 | 18.47 | 71.3 |

| EFCI-CMM (most critical switch: ER)  | 49.39 | 25.33 | 23.13 | 89.2 |

| CMM-EFCI (least critical switch: ER) | 40.43 | 26.14 | 24.25 | 78.0 |

| All CMM                              | 51.63 | 25.72 | 25.72 | 99.2 |

Table 4. Throughput of all groups under the various combinations of switch schemes.

ments are tabulated in Table 3. To clearly display the advantages and weaknesses of various switches, ranking is used instead of the real value. From the table we observe that EPRCA is the best in utilization and the worst in MQL and fairness. The Max-Min schemes can achieve better fairness. The performance of ERICA and CAPC is medium. In summary, from the ranking of utilization, MQL, and fairness, we feel that CMM is a better scheme.

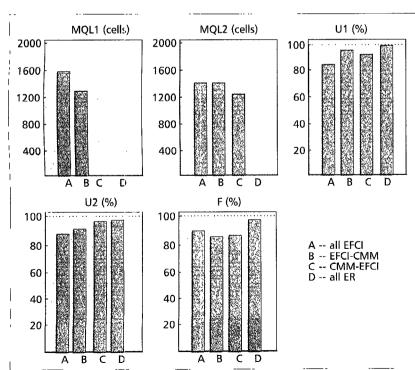

Figure 9. Comparison of the various switch schemes in the configuration (NI = 0, N2 = 2, N3 = 2).

# Location of the ER Switch

In this section, we want to investigate the location at which ER switches should be placed in mixed EFCI-ER environments. To save space, the CMM scheme is used to represent the various ER switches because of its good performance. Some simulations are done on various configurations. From the simulation results, a few rules are given to help us place the ER switch in EFCI-ER environments.

Bottleneck vs. Nonbottleneck: N1 = 0, N2 = 2, N3 = 2— Two VCs travel through link 2 only, and the other two VCs travel through both links 1 and 2. In this case, switch 2 is the bottleneck. The simulation results are shown in ig. 9. We observe that performance is better when the ER

Fig. 9. We observe that performance is better when the ER scheme is placed in the bottleneck switch. This placement can produce the same results as when all switches adopt the CMM scheme. On the other hand, if the ER switches are placed at nonbottleneck points, their functions are not fully utilized. We can see that placement of the ER switch at a nonbottleneck point has no effect in our simulation.

There is another important reason for this arrangement.

Under this configuration, if the algorithm at the bottleneck switch is substantially more oscillatory than the algorithm at the nonbottleneck switch, the rate mismatch problem occurs, causing unfairness [20].

Most Critical vs. least Critical: N1 = 2, N2 = 4, N3 = 2 — Under this configuration, the number of VCs passing through link 1 is 4, and the number passing through link 2 is 6. First, we define the the term critical. The most critical switch for a VC can be described as a switch that gives the source the lowest fair share based on the max-min fairness criteria. Similarly, the least critical switch is the one that gives the highest fair share in the VC's path. In our experiment, switch 1 is the least critical switch, switch 2 the most critical.

The simulation results are shown in Fig. 10. The total utilization of both switches (U1+U2) of EFCI-CMM placement is higher than that of CMM-EFCI placement. Also, the fairness degree of EFCI-CMM is obviously larger than that of CMM-EFCI placement. Hence, we suggest that an ER switch ought to be placed at the most critical point first. This conclusion is completely opposite to another

study in [21], which suggested that an ER switch should be placed at the least critical point first because it can relieve the severe beat down problem more.

From Table 4, the throughput of G3 is actually higher when the ER scheme is imposed on the least critical switch than when it is imposed on the most critical switch. Therefore, we should place the ER switch at the least critical point in view of the beat down problem [21]. However, the extra bandwidth of G3 is mainly obtained from the bandwidth released by G1. In fact, much bandwidth is wasted, while just a little bandwidth is used by G3.

Therefore, it is our opinion that an ER switch ought to be placed at the most critical point first. This placement can produce smaller maximum queue length, a larger degree of fairness, and higher throughput, although the beat down problem remains serious.

Near Source vs. Near Destination: Nl = 2, N2 = 2, N3 = 2 — In this case, performance is better when the

ER switch is located near the source, from Fig. 11. This is because lots of ER schemes (except for CMM and TMM) record the information from the forward RM cell, and modify the ER field on the backward path. Hence, newer information is received at the ER switch, and quicker feedback is sent to the source when the ER switch is near the source. On the other hand, the EFCI switch marks each forward

■ Figure 10. Comparison of the various switch schemes in the configuration (N1 = 2, N2 = 4, N3 = 2).

data cell when congestion occurs, and does not do anything on the backward path. Thus, when it is placed near the source, the propagation delay increases, which causes slower response at the source.

Under the configurations described above, we can determine how to place the ER switch. However, there may be some conflicts. For example, a backbone switch is generally

the bottleneck and most critical point, and is also far from the source. According to the simulation results (Figs. 9–11), we set the priority order as bottleneck > critical > distance. That is, we feel that a backbone switch should be considered first to have ER capacity. Nevertheless, ER switches should replace EFCI switches whenever possible everywhere in the network.

# Future Work

There are a number of ways to further extend research work on the interoperability issues discussed in this article. The first is to conduct more simulation experiments in a larger variety of configurations and under different traffic patterns. In particular, a performance comparison in the presence of intermittent and greedy flows might be useful. Another is the interoperability of the newly developed ER schemes and EFCI switches. Currently some new algorithms to set the ER field have been developed [25-27]. These algorithms should be verified in heterogeneous environments. Last, the interoperability among various ER switches is also worth research. After the transition from first- to second- generation switches, all switches may be equipped with ER function. The cooperation or conflict among different ER schemes should be studied.

Figure 11. Comparison of the various switch schemes in the configuration (N1 = 2, N2 = 2, N3 = 2).

# References

ATM Forum, "ATM Forum Traffic Forum Traffic Management Specification Version 4.0," ATM Forum af-tm-0056.000, Apr. 1996.

B. Flavio and W. F. Kerry, "The Rate-Based Flow Control Framework for the

Available Bit Rate ATM service," IEEE Network, vol. 9, no. 2, Mar. 1995,

pp. 25-39.

[3] S. Floyd and A. Romanow, "Dynamics of TCP Traffic over ATM Networks," Proc. ACM Sigcomm '94, Sept. 1994, pp. 79-88.

[4] C. M. Ozveren, R. Simcoe, and G. Varghese, "Reliable and Efficient Hop-by-Hop Flow Control," IEEE JSAC, vol. 13, no. 4, May 1995, pp. 642-50.

[5] H. T. Kung and R. Morris, "Credit-Based Flow Control for ATM Networks," IEEE Network, vol. 9, no. 2, Mar. 1995, pp. 40-48.

[6] R. Jain, "Congestion Control and Traffic Management in ATM Networks: Pacent Advances and A Survey." Comp. Networks and ISDN Sys., vol. 28. Recent Advances and A Survey," no. 13, Oct. 1996, pp. 1723–38. Comp. Networks and ISDN Sys., vol. 28,

[7] P. Newman, "Backward Explicit Congestion Notification for ATM Local Area Networks," Proc. IEEE GLOBECOM, Dec. 1993, pp. 719–23.

[8] H. Ohsaki et al., "Rate-Based Congestion Control for ATM Networks," Comp.

Commun. Rev., Apr. 1995.

[9] D. Sisalem and H. Schulzrinne, "Switch Mechanisms for the ABR Service: A

Comparison Study," http://www.lirmm.fr/atm/articles.html, June 1996. [10] A. Kolarov and G. Ramamurhy, "Comparison of ER and EFCI Flow Control Scheme for ABR Service in Wide Area Networks," *Proc. IFIP Broadband* Commun., Apr. 1995.

[11] L. Gerda and O. Casals, "A Simulation Study of Switching Mechanisms for ABR Service in ATM Networks," interim rep. UPC-DAC-1996-21, Feb. 1996.

[12] ITU-T SG 13, "Traffic Control and Congestion Control in B-ISDN," Draft Rec. I.371, Nov. 1995.

[13] H. Saito, et al., "Performance Issues in Public ABR Service," IEEE Commun.

[13] H. Saito, et al., "Performance Issues in Public ABR Service," IEEE Commun. Mag., vol. 34, no. 11, Nov. 1996, pp. 40–48.

[14] N. Yin and M. G. Hluchy, "On Closed-Loop Rate Control for ATM Cell Relay Networks," Proc. IEEE INFOCOM '94, 1994, pp. 99–108.

[15] L. Roberts, "Enhanced Proportional Rate Control Algorithm," ATM Forum 94-0735R1, Aug. 1994.

[16] R. Jain et al., "The ERICA Switch Algorithm: A Complete Description," ATM Forum 96-1172, Aug. 1996.

[17] A. W. Barnhart, "Explicit Rate Performance Evaluations," ATM Forum 94-0983, Oct. 1994.

0983, Oct. 1994

[18] A. Charny, K. K. Ramakrishnan, and A. Lauck, "Time Scale Analysis and Scalability Issues for Explicit Rate Allocation in ATM Networks," IEEE/ACM

Trans. Networking, vol. 4, no. 4, Aug. 1996, pp. 569–81.

[19] D. H. K. Tsang and W. K. F. Wong, "A New Rate-Based Switch Algorithm for ABR Traffic to Achieve Max-Min Fairness with Analytical Approximation and Delay Adjustment," Proc. IEEE INFOCOM '96, 1996, pp. 1174-81.

[20] N. T. Plotkin and J. J. Sydir, "The Rate Mismatch Problem in Heterogeneous ABR Flow Control," Proc. IEEE INFOCOM '97, 1997.

[21] Y. Chang, N. Golmie, and David Su, "Study of Interoperability between

EFCI and ER Switch Mechanisms for ABR Traffic in an ATM Network," Proc.

4th Int'l Conf. Comp. Commun. and Networks, 1995, pp. 310–15.

[22] A. Arulambalam, X. Chen, and N. Ansari, "Allocating Fair Rates for Available Bit Rate Service in ATM Networks," IEEE Commun. Mag., vol. 34, no.

11, Nov. 1996, pp. 92–100. [23] Y. C. Lai and Y. D. Lin, "Performance Analysis of Rate-based Congestion Control Scheme and Choice of High and Low Thresholds," Proc. 6th Int'l. Conf. Comp. Commun. and Networks, Sept. 1997, pp. 70–75. [24] Y. C. Lai and Y. D. Lin, "Performance Analysis of Rate-Based Flow Control

under a Variable Number of Sources," Comp. Networks and ISDN Syst., to

[25] F. M. Chiussi et al., "Explicit Rate ABR Schemes Using Traffic Load as Congestion Indicator," Proc. 6th Int'l. Conf. Comp. Commun. and Networks, Sept. 1997, pp. 76–84.

[26] L. Kalampoukas, A. Varma, and K. K. Ramakrishnan, "An Efficient Rate Allocation Algorithm for ATM Networks Providing Max-Min Fairness," Proc. 6th IFIP Int'l. Conf. High Perf. Networking, Sept. 1995. pp. 143–54.

[27] A. Arulambalam, X. Chen, and N. Ansari, "An Intelligent Explicit Rate Con-

trol Algorithm for Available Bit Rate Services in ATM Networks," Proc. ICC '97, June 1997, pp. 200-4.

### Biographies

YUAN-CHENG LAI (gis83802@cis.nctu.edu.tw) received B.S. and M.S. degrees in computer science and information engineering from National Taiwan University in 1988 and 1990, respectively. From 1992 to 1994 he was an associate researcher at the Computer and Communication Research Laboratoriess of the Industrial Technology Research Institute, Taiwan. He is currently finishing his Ph.D. in the Department of Computer and Information Science at National Chiao Tung University. His research interests are in design, management, and analysis of ATM networks, queueing theory, and multimedia communications.

YING-DAR LIN [M] (ydlin@cis.nctu.edu.tw) received a Bachelor's degree in computer science and information engineering from National Taiwan University in 1988, and M.S. and Ph.D. degrees in computer science from the University of California, Los Angeles, in 1990 and 1993, respectively. At the UCLA Computer Science Department, he worked as a research assistant from 1989 to 1993 and as a teaching assistant from 1991 to 1992. He joined the faculty of the Department. ment of Computer and Information Science at National Chiao Tung University in August 1993 and is now associate professor. His research interests include design and analysis of high-speed LANs/MANs/WANs, traffic characterization, service and network management, and network-centric computing.